# Germanium Photodetector with Monolithically Integrated Narrowband Matching Network on a Silicon Photonics Platform

Laurens Bogaert<sup>1,2,\*</sup>, Jochem Verbist<sup>1,2</sup>, Kasper Van Gasse<sup>1</sup>, Guy Torfs<sup>2</sup>, Johan Bauwelinck<sup>2</sup>, and Gunther Roelkens<sup>1</sup>

<sup>1</sup> Photonics Research Group, Dept. INTEC, Ghent University–Imec, Technologiepark 126, 9052 Ghent, Belgium <sup>2</sup> IDLab, Dept. INTEC, Ghent University–Imec, Technologiepark 126, 9052 Ghent, Belgium \*e-mail: Laurens.Bogaert@ugent.be

# **ABSTRACT**

High data rate transceivers typically consist of a system with hybrid integration of the electronics and photonics. Impedance levels provided by the opto-electronic device are often not the same as the levels desired by the electronic circuit. This mismatch introduces suboptimal operation and can even be detrimental for the overall system performance. Consequently, a matching circuit is often implemented on the electronic IC together with the main electronic functionality. Direct RF matching of the opto-electronic devices on the photonic IC has the potential to significantly reduce the overall system cost as the area cost of photonic chips is much lower. In this paper, narrowband LC-matching is shown for a germanium photodetector on the iSiPP50G silicon photonics platform to convert the output impedance to a more standard 50  $\Omega$  impedance level at 30 GHz. By tuning the photodetector reverse biasing voltage between 0 Volt and 3 Volt, a reflection coefficient lower than -20 dB is obtained over the frequency range between 24.3 and 30.4 GHz.

Keywords: Capacitors, Inductors, Narrowband matching, Photodetector, Radio-over-Fiber, Silicon photonics

### 1. INTRODUCTION

High data rate transceivers often make use of a complex architecture including photonics as well as electronics and typically hybrid integration is implemented where the electronic chip (EIC) and photonic chip (PIC) are manufactured separately. Opto-electronic conversion is required in the PIC to convert the data from the optical to the electrical domain and vice versa. This opto-electronic device (photodetector, electro-absorption modulator, etc.) serves as an interface to the EIC but typically has an impedance mismatch compared to the input or output impedance of the EIC. This can result in strong reflections, potential instabilities, etc. Consequently, a matching network is designed and this is typically done together with the main electronic system on the EIC. This is however suboptimal as the EIC, especially for the more advanced technology nodes, is substantially more expensive compared to the PIC [1]. The iSiPP50G silicon photonics platform includes two metal layers and consequently enables monolithic integration of RF passives on the PIC [1]-[2]. In this paper, we will focus on the narrowband matching of a Ge-on-Si photodetector but firstly the relevant active devices (Ge photodetector) and passive devices (inductors and capacitors) will be discussed.

# 2. GERMANIUM PHOTODETECTOR

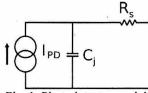

In this paper, narrowband matching of a Ge photodetector on the iSiPP50G silicon photonics platform will be discussed. For narrowband applications, a simplified model can be used (Fig. 1, [2]). This model consists of a current source in combination with an RC filter where the junction capacitance  $C_j$  varies with the applied reverse voltage and where the series resistance  $R_s$  is nearly voltage independent. The matching network was designed using the nominal values at 2 Volt reverse biasing of the adopted Ge photodetector:  $R_s \approx 35 \Omega$  and  $C_j \approx 35 \text{ fF}$ .

Fig. 1. Photodetector model

## 3. RF PASSIVES

Passive RF components are bulky and it is therefore advantageous to move them to the PIC where the cost per surface area is substantially lower. In this work, the commercial silicon photonics platform iSiPP50G from imec is being used to demonstrate a monolithically integrated matching network. The stack of this technology platform includes two metal layers and therefore allows for the introduction of RF passives on the PIC.

## 3.1 Capacitors

The back end of line of the iSiPP50G silicon photonics platform includes two metal layers (Cu) separated by an oxide (SiO<sub>2</sub>). Consequently, parallel plate MIM (metal-insulator-metal) capacitors are readily available in iSiPP50G. The capacitance value [3] can be approximated by using equation (1) where  $\varepsilon_0$ ,  $\varepsilon_r$  and t are fixed (respectively the permittivity of vacuum, the relative permittivity and the thickness of the oxide) and where the parallel plate overlap area A can be adjusted to size the capacitance. The second term in the approximation is a correction term to roughly include the fringe effects (with P the perimeter of the parallel plates). For the given technology platform, the formula approximates 69 aF x A [ $\mu$ m<sup>2</sup>] + 34 aF x P [ $\mu$ m]. Measured values are approximately 10 to 15 percent lower than what is expected from this approximation. This can be attributed to an overestimation of the relative permittivity of the SiO<sub>2</sub> or an underestimation of the oxide thickness.

$$C = \frac{\epsilon_0 \epsilon_r A}{t} + \epsilon_0 \epsilon_r P \tag{1}$$

Secondly, the capacitors are to be used in high-speed systems. Consequently, the self-resonant frequency (SRF) should be sufficiently high. This is done by placing the parallel plate capacitor in between the bondpads to minimize the lead length and therefore maximize the SRF.

#### 3.2 Inductors

A second important building block in lossless matching networks are spiral inductors [3]. The presence of a second metal layer allows for multi-turn spiral inductors largely extending the range of feasible inductances. The design parameters for such spiral inductors are the trace width, the spacing between turns, the radius of the inner turn and the number of turns. Minimizing the number of turns is desirable for high-speed applications to minimize the inter-winding capacitance and consequently maximize the SRF. Secondly, it is beneficial to implement the inductors on the top metal layer to minimize capacitive coupling to the substrate. The bottom metal layer is only being used to avoid crossings in multi-turn inductors. Inductors are quite predictable as they are defined by their geometry rather than the technology stack. The inductor is modelled by a series inductor-resistor combination where the losses are typically described using a Q-factor. The Q-factor represents the ratio of the imaginary and real part of the inductor impedance and is frequency dependent.

# 4. NARROWBAND RF MATCHING

In this section, the results of a narrowband matched germanium photodiode will be discussed. The target impedance in this design is a standard 50  $\Omega$  impedance at 30 GHz. A first order LC matching network is adopted in a low pass configuration to allow for external biasing of the photodetector.

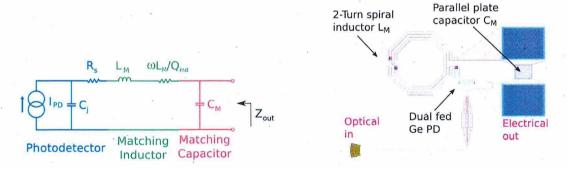

Fig. 2. LC matched photodetector; (left) equivalent network; (right) layout of the implemented design

Figure 2 depicts the implemented matching network where the finite losses of the inductor are included in the model and  $\omega$  denotes the angular frequency. The impedance seen at the output of the PIC is given in equation (2). This equation is solved for a given target impedance (e.g. 50  $\Omega$ ) at a certain frequency (e.g. 30 GHz) to find the desired inductance and capacitance values. Because of the a priori unknown Q-factor, this design process is iterative. The design starts from a photodetector with a junction capacitance of 35 fF and a series resistance of about 35  $\Omega$ . The designed matching network consists of a two turn spiral inductor (simulated inductance and Q-factor of respectively 730 pH and 17 at 30 GHz), lead inductances caused by the traces (around 170 pH) and a parallel plate capacitor (55 fF). Measuring the standalone variants of the implemented passives show that the

inductance value of the spiral inductor (718 pH) and the capacitance of the parallel plate capacitor (53 fF) closely match the simulated values.

$$Z_{out} = \frac{1}{j\omega C_M} || \left[ \left( j\omega L_M + \frac{\omega L_M}{Q_{ind}} \right) + R_s + \frac{1}{j\omega C_j} \right]$$

(2)

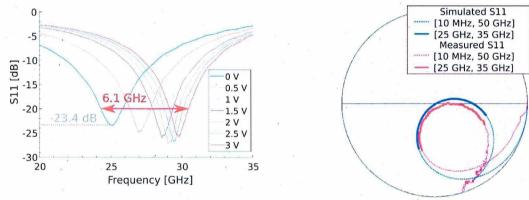

The performance of the matching network can be evaluated by looking at the output impedance or equivalently the output reflection coefficient  $S_{11}$  (which is shown in Fig 3). It can be seen that by changing the reverse biasing of the photodetector the frequency of optimal matching can be tuned over a wide range and that higher reverse voltages result in matching at higher frequencies due to the reduction in junction capacitance  $C_j$  of the photodetector. The junction capacitance for the measured wafer was higher than the nominal values used for the design of the matching network and therefore results in a shift of the matching frequency to somewhat lower values. This can be partially compensated for by increasing the reverse voltage. For future designs, the matching network, should be designed for the capacitance value at a lower reverse voltage (e.g. 1 V) such that correction capabilities for process variations are maximized. By tuning the photodetector reverse biasing voltage between 0 and 3 Volt, a reflection coefficient lower than -20 dB is obtained over the frequency range between 24.3 and 30.4 GHz. Simulations and measurements show similar results and the discrepancies can be explained by process tolerances and the fact that a simple photodetector model was used (Fig. 1) which does not include low frequency effects.

Fig. 3. (left) Reflection coefficient at the output of the LC matched Ge photodetector as a function of the reverse bias; (right) Comparison between the measured S11 at 3V and the simulated S11 using nominal values

# 5. CONCLUSIONS

Providing matched impedance levels at the interface between electronic and photonic ICs is typically taken care of at the electronic side. A more cost-effective way to implement this is by adding the RF passives on the silicon photonics IC. Here we demonstrate a first order low pass LC matching network monolithically cointegrated with a germanium photodetector on the iSiPP50G silicon photonics platform. Reflection coefficients lower than -20 dB are obtained between 24.3 and 30.4 GHz by tuning the biasing level of the photodetector between 0 and 3 volt. The capabilities of on-PIC RF passive circuit design are not limited to matching circuits (e.g. embedded bias tees) and can help to implement some of the basic RF functionality in a more cost-effective way.

# **ACKNOWLEDGEMENTS**

This work was supported by the Ghent University Special Research Fund (BOF14/GOA/034), the Methusalem funding of the Flemish government, the Air Force Office of Scientific Research (AFOSR) (FA95501810015), and by the European Research Council under Grant 695495 (ATTO).

# REFERENCES

- [1] M.S. Nezami, et al.: Integrated RF Passive Low-Pass Filters in Silicon Photonics, *IEEE Photon. Technol. Lett.*, vol. 30, pp. 2052-2055, Dec. 2018.

- [2] A. Novack, *et al.*: Germanium photodetector with 60 GHz bandwidth using inductive gain peaking, *Opt. Express*, vol. 21. pp. 28387-28393, 2013.

- [3] T. H. Lee: The Design of CMOS Radio-Frequency Integrated Circuits, *Cambridge University Press*, 2<sup>nd</sup> Edition